Application note 5SYA 2032-04

## **Applying IGCTs**

The Integrated Gate Commutated Thyristor (IGCT) has become the power semiconductor of choice in medium voltage industrial applications. Also in energy management and the traction markets, the versatility of this power switch has enabled performance improvements and cost savings in a variety of applications.

### 1. Introduction

The outstanding feature of the IGCT - leading to its name and its main advantages - is not only the silicon wafer itself, but the way it is driven by the gate - the electrical and mechanical gate-drive design. The «hard- drive» concept at the heart of IGCT operation requires the mechanical integration of gate driver and semiconductor into one single unit with low circuit inductance. It also implies a number of new converter features, which make IGCT converters different from GTO or IGBT converters. It is the scope of this application note to make designers familiar with the data sheets and the use of IGCTs in their main application areas.

The following features are important to remember:

- no turn-off snubber is needed in applications without series connection; where turn-off snubbers are used, they are considerably smaller than those of GTOs

- the customer control interface is reduced to a power supply, an optical control input and an optical status feedback output

- gate drive geometry is an important parameter in mechanical stack design.

It should be noted that «IGCT» is a generic reference to the complete device. «GCT» refers to the semiconductor press-pack component. Further distinctions can be made to distinguish RC-IGCTs (reverse- conducting), RB-IGCTs (reverse blocking) and AS-IGCTs (asymmetric with neither reverse blocking nor reverse-conducting capability). Hitachi Energy sells only IGCTs whereas other manufacturers may offer the GCT and gate-unit separately. The term «SGCT» is also used by some suppliers to designate a «symmetric blocking» device, known here as RB-IGCT per the above definition.

This application note covers the asymmetric and reverse conducting IGCTs. The first part is a user's guide to IGCT data sheets. In the second part application-specific topics are illustrated.

# Table of contents

| 001        | Introduction                                                                                       |

|------------|----------------------------------------------------------------------------------------------------|

| 003        | Datasheet user's guide                                                                             |

| 003        | Key parameters and features                                                                        |

| 003        | Blocking                                                                                           |

| 003        | Mechanical data                                                                                    |

| 004        | GCT data                                                                                           |

| 004        | On-state of IGCT                                                                                   |

| 004        | Turn-on switching                                                                                  |

| 007        | Turn-off switching                                                                                 |

| 008        | Gate unit data                                                                                     |

| 008        | Power supply                                                                                       |

| 008        | Optical control input/output                                                                       |

| 009        | Connectors                                                                                         |

| 009        | Visual feedback                                                                                    |

| 009        | Thermal                                                                                            |

| 010        |                                                                                                    |

| 010        | Diagrams                                                                                           |

| 010        | GCT on-state current vs. on-state voltage                                                          |

|            | GCT surge current vs pulse width and number of pulses<br>GCT turn-off characteristics              |

| 011        |                                                                                                    |

| 012        | Gate unit related diagrams                                                                         |

| 013        | Diode-specific data of reverse conducting IGCTs (from datsheet 5SHX 26L4510)                       |

| 013        | Diode On-state                                                                                     |

| 013        | Diode turn-on                                                                                      |

| 013        | Diode turn-off                                                                                     |

| 013        | Thermal data                                                                                       |

| 013        | IGCT application-specific topics                                                                   |

| 013<br>014 | IGCTs in voltage source Inverters (VSI)                                                            |

| 014        | Design criteria                                                                                    |

| 015        | Determining the design parameters                                                                  |

| 015        | Determining the value of the di/dt limiting inductor                                               |

| 015        | Determining the value of the clamp capacitor CCL and the damping resistor RS                       |

| 016        | Stray inductance LCL                                                                               |

| 018        | Influence of the clamp diode type<br>Overview of parameter influences                              |

| 018        | Use of additional snubber                                                                          |

| 018        | Retriggering of an IGCT                                                                            |

| 019        |                                                                                                    |

| 019        | When are external retrigger pulses required?                                                       |

| 019        |                                                                                                    |

| 020        | How are external retrigger pulses released?<br>What is the best timing for the external retrigger? |

| 020        | Applications requiring retrigger pulses                                                            |

| 020        | Series connection of IGCTs                                                                         |

| 022        | Design criteria                                                                                    |

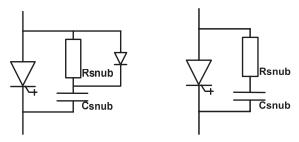

| 022        | Snubber concepts                                                                                   |

| 022        | Scaling of clamp design                                                                            |

| 022        | Factors influencing turn-off voltage sharing                                                       |

| 022        | Variations of IGCT parameters                                                                      |

| 022        | Variations of converters parameters                                                                |

| 023        | Optional anode voltage monitoring                                                                  |

| 024        | Conclusions                                                                                        |

| 024        | Protection                                                                                         |

| 024        | Consequence of a GCT or diode failure in a 3-level phase-leg (example)                             |

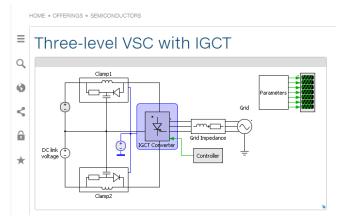

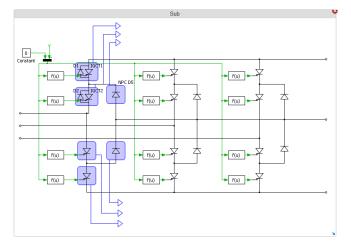

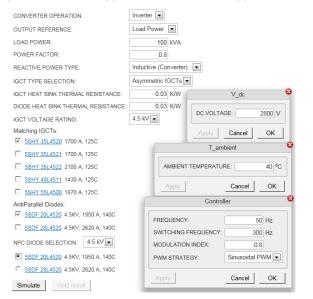

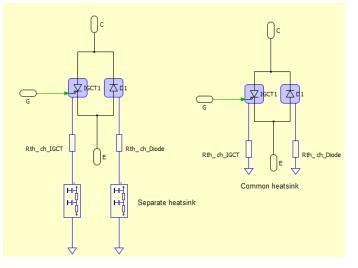

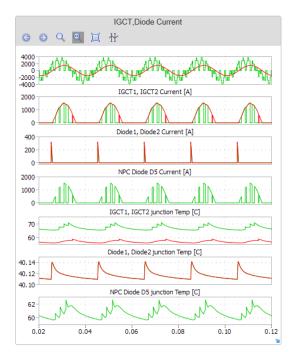

| 024        | IGCT losses and thermal calculations using the SEMIS Tool                                          |

| 025        | Glossary                                                                                           |

| 027        | References                                                                                         |

| 027        | Revision history                                                                                   |

|            |                                                                                                    |

### 2. Data sheet user's guide

This section is a detailed guide to the correct understanding of an IGCT data sheet. Parameters and ratings will be defined and illustrated by figures where appropriate, while following the sequence in which parameters appear in the data sheet. For explanation purposes, data and diagrams associated with IGCT type 5SHY 55L4500 have been used, but because all IGCTs have similar data sheets, this guide is applicable to all IGCTs. Additionally a 5SHX 26L4520 data sheet is used to explain the diode parameters of reverse-conducting devices. The data sheets distinguish between maximum rated values and characteristic values. Maximum rated values indicate limits beyond which damage to the device may occur. Characteristic values are parameters defined under typical application conditions.

Hitachi Energy reserves the right to change data sheets without notice. Therefore, for the latest version, please visit our website at www.hitachienergy.com/semiconductors.

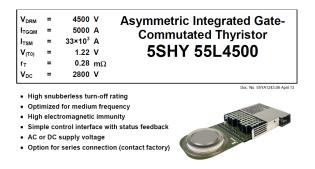

### 2.1. Key parameters and features

These key features briefly describe the IGCT without reference to operating conditions. The data presented here also appears in the corresponding section of the data sheet, together with operating or test conditions. For example,  $I_{TSM} = 33 \times 103$  A can also be found in the on-state section, where this value applies at  $t_p = 10$  ms and  $T_{vj} = 125$  °C, with zero reapplied voltage.

### 2.2. Blocking

### Maximum rated values

| Parameter                                                     | Symbol              | Conditions                                                                         | min t | ур | max  | Unit |

|---------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------|-------|----|------|------|

| Rep. peak off-<br>state voltage                               | V <sub>drm</sub>    | Gate unit<br>energized                                                             |       |    | 4500 | V    |

| Permanent DC<br>voltage for 100<br>FIT failure rate<br>of GCT | V <sub>DClink</sub> | Ambient cosmic<br>radiation at sea<br>level in open air.<br>Gate unit<br>energized |       |    | 2800 | V    |

| Reverse voltage                                               | V <sub>RRM</sub>    | IGCT in off-state                                                                  |       |    | 17   | V    |

Characteristic values

| Parameter                       | Symbol           | Conditions                                       | min | typ | max | Unit |

|---------------------------------|------------------|--------------------------------------------------|-----|-----|-----|------|

| Rep. peak off-<br>state current | I <sub>DRM</sub> | $V_{\rm D} = V_{\rm DRM}$<br>Gate unit energized |     |     | 50  | mA   |

$V_{\text{DRM}}$ :  $V_{\text{DRM}}$  is the maximum repetitive voltage in the forward direction. The IGCT is able to block this voltage at line frequencies of 50 or 60 Hz, assuming a sinusoidal voltage waveform.  $V_{\text{DRM}}$  is a maximum rating; if exceeded, leakage current and power loss may increase rapidly and may lead to thermal runaway and subsequent blocking degradation. Although  $V_{\text{DRM}}$  specifies the IGCT's quasi-static blocking capability, it is, in fact, the maximum dynamic voltage,  $V_{\text{DM}}$ , that IGCTs can withstand following turn-off. It is important to note that the IGCT can only block rated voltage if the gate unit is energized.

$V_{DC-link}$ :  $V_{DC-link}$  is the maximum continuous DC voltage for a specified failure rate (100 FIT for example), due to cosmic radiation. Exceeding this voltage does not immediately lead to device failure, but the probability of a cosmic radiation failure increases progressively with applied DC voltage. A detailed explanation and IGCT type-specific calculations are printed in the application note 5SYA 2046 «Failure rate of IGCTs due to cosmic rays».

$V_{\text{RRM}}$ :  $V_{\text{RRM}}$  is the maximum repetitive voltage in the reverse direction. For all asymmetric IGCTs, this value is in the range of 17 V. It is determined by the reverse blocking capability of the gate-to-cathode junction ( $V_{\text{GRM}}$ ).

$I_{_{DRM}}$ :  $I_{_{DRM}}$  specifies the maximum leakage current, when  $V_{_{DRM}}$  is applied. It is measured at  $T_{_{vj \, max}}$ , with sinusoidal voltage pulses ( $t_{_{o}} = 10 \text{ ms}$ ) and an energized gate unit.

### 2.3. Mechanical data

Maximum rated values

| Parameter      | Symbol | Conditions | min | typ | max | Unit |

|----------------|--------|------------|-----|-----|-----|------|

| Mounting force | Fm     |            | 36  | 40  | 44  | kN   |

We reserve the right to make technical changes or modify the contents of this document without prior notice. With regard to purchase orders, the agreed particulars shall prevail. Hitachi Energy Ltd. does not accept any responsibility whatsoever for potential errors or possible lack of information in this document. We reserve all rights in this document and in the subject matter and illustrations contained therein. Any reproduction, disclosure to third parties or utilization of its contents – in whole or in parts – is forbidden without prior written consent of Hitachi Energy Ltd.

salesdesksem@hitachienergy.com

### Characteristic values

| Parameter                    | Symbol         | Conditions    | min  | typ | max  | Unit |

|------------------------------|----------------|---------------|------|-----|------|------|

| Pole-piece<br>diameter       | D <sub>p</sub> | ± 0.1 mm      |      | 85  |      | mm   |

| Housing thickness            | Н              |               | 25.3 |     | 25.8 | mm   |

| Weight                       | m              |               |      |     | 2.9  | Kg   |

| Surface creepage<br>distance | D <sub>s</sub> | Anode to gate | 33   |     |      | m    |

| Air strike distance          | D <sub>a</sub> | Anode to gate | 10   |     |      | mm   |

| Length                       | I              | ± 1.0 mm      |      |     | 439  | m    |

| Height                       | h              | ± 1.0 mm      |      |     | 41   | mm   |

| Width IGCT                   | W              | ± 1.0 mm      |      |     | 173  | mm   |

F<sub>m</sub>: F<sub>m</sub> is the mounting force necessary to establish a good electrical and thermal contact. It is very important that  ${\rm F}_{\rm m}$  stays within the specified limits, even under limiting operating temperature. Thermal expansions and tolerances of stack parts have to be considered in the design of the clamping system. Too low a mounting force results in increased thermal resistance and particularly at high currents - in damage to the dry interfaces within the housing that may provoke degradation. Also the individual cathode segments might not all be correctly contacted, leading to an increase in V<sub> $\tau$ </sub> and drastic reduction of I<sub>TSM</sub> and I<sub>TGOM</sub>. Exceeding F<sub>m</sub> leads to increased mechanical stress on the silicon wafer, particularly where thermal cycling is severe. This reduces life-expectancy of the device and can lead to premature wear-out of the cathode segment metallization with subsequent gate-tocathode short circuits. Besides a correct mounting force, it is also vital that the pressure is distributed homogeneously over the contact area. If not, the copper pole pieces of the housing may deform plastically, which in turn, may lead to localized mechanical stress on the silicon wafer with subsequent degradation of the device performance or even fracturing of the wafer. Details concerning a correct clamping system are described in application note 5SYA 2036 «Recommendations regarding mechanical clamping of press pack high power semiconductors».

**Note:** If no external force is applied across a press-pack semiconductor, the silicon wafer will probably not contact the pole pieces at all. For even the most basic device verifications (blocking or gating checks by service personnel), a minimum clamping force of about 1 kN is required to establish contact for low-current measurements. m: The weight of the complete device, including the gate unit.

$\rm D_s$ : The surface creepage distance is defined as the shortest path along the ceramic surface between the anode flange and the gate contact.

$\mathsf{D}_{\mathsf{a}}$  : The air strike distance is defined as the shortest direct path between the anode side and the gate contact.

$I_{T(AV)M}$ ,  $I_{T(RMS)}$ : The max. average and root-mean-square on-state currents, respectively. These values are established with given boundary conditions.  $I_{T(AV)M}$  and  $I_{T(RMS)}$  are the average and RMS values of the half-sinusoidal on-state current when the junction operates at its maximum temperature with the case temperature fixed at a given value, here 85 °C.

These figures give a comparative value for current handling capability at low frequency (negligible switching losses). They are mainly used to compare different products for on-state performance and they indicate a maximum current capability for the defined temperatures. As with all comparisons, the thermal conditions must be considered as they may differ from product to product and between suppliers, which substantially influences the current ratings.

### 2.4. GCT Data 2.4.1. On-state of IGCT

Maximum rated values

| Parameter                                                | Symbol                 | Conditions                                                                              | min typ | max                  | Unit             |

|----------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------|---------|----------------------|------------------|

| Max. average on-<br>state current                        | l<br><sub>T(AV)M</sub> | Half sine wave                                                                          |         | 1870                 | A                |

| Max. RMS on-<br>state current                            | l<br>T(RMS)            | T <sub>c</sub> = 85 °C<br>Double side<br>cooled                                         |         | 2940                 | A                |

| Max. peak non-<br>repetitive surge<br>on-state current   | I <sub>tsm</sub>       | $t_p = 3 \text{ ms}, T_i =$<br>125 °C, sine half<br>wave,<br>$V_p = V_R = 0 \text{ V},$ |         | 50×10 <sup>3</sup>   | A                |

| Limiting load<br>integral                                | l²t                    | after surge                                                                             |         | 3.75×10 <sup>6</sup> | A <sup>2</sup> s |

| Max. peak<br>non-repetitive<br>surge on-state<br>current | I <sub>tsm</sub>       | tp = 10 ms<br>T <sub>i</sub> = 125 °C, sine<br>wave after surge: .                      |         | 33×10 <sup>3</sup>   | A                |

| Limiting load<br>integral                                | l²t                    | $V_{\rm D} = V_{\rm R} = 0$ V                                                           |         | 5.45×106             | A <sup>2</sup> s |

Hitachi Energy Switzerland Ltd. Semiconductors Fabrikstrasse 3 5600 Lenzburg, Switzerland Tel: +41 58 586 10 00 salesdesksem@hitachienergy.com We reserve the right to make technical changes or modify the contents of this document without prior notice. With regard to purchase orders, the agreed particulars shall prevail. Hitachi Energy Ltd. does not accept any responsibility whatsoever for potential errors or possible lack of information in this document.

| Parameter                                                   | Symbol                            | Conditions                                                                                       | min ty | /p max               | Unit             |

|-------------------------------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------|--------|----------------------|------------------|

| Max. peak non-<br>repetitive surge<br>on-state current      | I <sub>tsm</sub>                  | t <sub>p</sub> = 30 ms,<br>T <sub>i</sub> = 125 °C, sine .                                       |        | 22×10 <sup>3</sup>   | A                |

| Limiting load<br>integral 30 ms                             | l²t                               | wave after surge:<br>$V_{D} = V_{R} = 0 V$                                                       |        | 7.26×10 <sup>6</sup> | A <sup>2</sup> s |

| Stray indutance<br>between GCT<br>and antiparallel<br>diode | LD                                | Only relevant for<br>applications with<br>antiparallel diode<br>to the IGCT                      |        | 300                  | nH               |

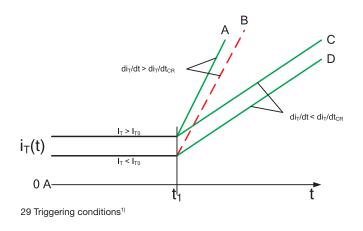

| Critical rate of<br>rise of on-state<br>current             | d <sub>iT</sub> /d <sub>tcr</sub> | For higher d /d,<br>and current lower<br>than 100 A an<br>external retrigger<br>puls is required |        | 200                  | A/µs             |

Characteristic values

| Parameter             | Symbol            | Conditions                                          | min  | typ | max  | Unit |

|-----------------------|-------------------|-----------------------------------------------------|------|-----|------|------|

| On-state<br>voltage   | V <sub>T</sub>    | I <sub>T</sub> = 4000 A,<br>T <sub>j</sub> = 125 °C | 2.15 |     | 2.35 | V    |

| Threshold<br>voltage  | V <sub>(T0)</sub> | T <sub>j</sub> = 125 °C<br>I <sub>T</sub> = 1000    | 1.12 |     | 1.22 | V    |

| Slope resis-<br>tance | r <sub>T</sub>    | 5000 A                                              | 0.24 |     | 0.28 | m    |

The user can easily calculate  $I_{_{T(AV)M}}$  and  $I_{_{T(RMS)}}$ , under varying conditions, from the following equations:

$$\begin{split} I_{T(AV)M} &= 2 \frac{\sqrt{V_{(T0)}^2 + r_T \cdot \pi^2 \cdot P_{(AV)M}} - V_{(T0)}}{r_T \cdot \pi^2} \quad \text{with} \\ P_{(AV)M} &= \frac{T_{vj \max} - T_C}{R_{th(jc)}} \\ I_{T(RMS)} &= I_{T(AV)M} \frac{\pi}{2} \end{split}$$

The definitions for I<sub>T(AV)M</sub> and <sub>IT(RMS)</sub> originate from classic phase control thyristor practice, which mainly applies to line frequency applications at 50 and 60 Hz. Since in most IGCT applications, the current waveforms are far from sinusoidal and the switching losses form a considerable part of total power losses, I<sub>T(AV)M</sub> and I<sub>T(RMS)</sub> have no real practical meaning. However, they may be useful for comparison with other products, as already mentioned.

$I_{\text{TSM}}$ : Max. non-repetitive surge current is the max. allowed and pulse-width dependent peak value of a half-sinusoidal surge current,

applied at an instant when the IGCT is operating at its maximum junction temperature. Although, in practice, the case temperature prior to a surge is always below 125 °C, both the junction and the housing are heated to 125 °C when the surge current limit is established. This worst-case test condition provides an additional margin to the real stress in an application. For surge current requirements that do not resemble a sine half wave or cannot be covered by a sine half wave shown in Fig. 8, please contact your nearest representative or the address shown at the end of this application note for evaluation.

During a surge, the junction heats up to a temperature well above its rated maximum value. Therefore, the thyristor is no longer able to block rated voltage, so the  $I_{TSM}$  values are valid only for  $V_{\rm D} = V_{\rm R} \approx 0$  V after the surge, i.e. without reapplied voltage. Though a single surge does not cause any irreversible damage to the silicon wafer, it should not be allowed to occur too frequently.

I<sup>2</sup>t: Limiting surge current load integral I<sup>2</sup>t is an abbreviation and stands for  $\int |T^2| dt$ . This value is derived from the I<sub>TSM</sub> value discussed above, according to the following expression:

$$I^{2}t = \int_{0}^{t_{p}} I_{T}^{2}(t) dt = \frac{I_{TSM}^{2} \cdot t_{p}}{2}$$

(for half-sinusoidal waveforms)

To protect the IGCT, the I<sup>2</sup>t of a semiconductor fuse must be lower than the maximum <sup>I2</sup>t of the IGCT. The constraints for  $I_{TSM}$  applies similarly to I<sup>2</sup>t.

$L_{\rm D}$ : Stray inductance between IGCT and anti-parallel diode: for optimized switching behavior, it is recommended to minimize  $L_{\rm D}$  as much as possible. Typical application values are in the range of 30...50 nH. However, in the data sheets for asymmetric IGCTs, a maximum  $L_{\rm D}$  is defined and was verified at operation.

$d_{rr}/d_{ter}$ . This is the critical rate of rise of forward current at IGCT turnon. Please refer to the detailed description in section 3.3.

$V_{\tau}$ :  $V_{\tau}$  is the on-state voltage at a given on-state current  $I_{\tau}$  (normally  $I_{_{TGQM}}$ ) and at maximum junction temperature.  $V_{\tau}$  is influenced, within limits, by the irradiation dose that determines minority carrier lifetime. A lower  $V_{\tau}$  automatically implies a higher  $E_{_{off}}$ , and vice versa. Maximum and typical values are shown.

$V_{(T0)}$ ,  $r_T$ : In many cases, it is convenient and sufficiently accurate to approximate the on-state characteristic (max. values) by a straight line, determined by  $V_{T0}$  and  $r_T$ :

$$V_T(I_T) = V_{(T0)} + I_T \cdot r_T$$

We reserve the right to make technical changes or modify the contents of this document without prior notice. With regard to purchase orders, the agreed particulars shall prevail. Hitachi Energy Ltd. does not accept any responsibility whatsoever for potential errors or possible lack of information in this document. We reserve all rights in this document and in the subject matter and illustrations contained therein. Any reproduction, disclosure to third parties or utilization of its contents – in whole or in parts – is forbidden without prior written consent of Hitachi Energy Ltd.

Hitachi Energy Switzerland Ltd.

salesdesksem@hitachienergy.com

5600 Lenzburg, Switzerland

Tel: +41 58 586 10 00

Semiconductors

Fabrikstrasse 3

The current range over which this expression yields acceptable accuracy is indicated by the condition  $I_T = 1000 - 5000 \text{ A}$  (e.g. 5SHY 55L4500).

When average and  $\rm R_{_{MS}}$  values of on-state current,  $\rm I_{_{T(AV)}}$  and  $\rm I_{_{T(RMS)}}$ , are known, the on-state power loss,  $\rm P_{_{on-state}}$ , is calculated using  $\rm V_{_{(T0)}}$  and rT:

$$P_{on-state} = V_{(T0)} \cdot I_{T(AV)} + r_T \cdot I_{T(RMS)}^2$$

### 2.4.2. Turn-on switching

### Maximum rated values

| Parameter                                       | Symbol                            | Conditions                                                                                                                                   | min | typ | max  | Unit |

|-------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| Critical rate of<br>rise of on-state<br>current | di <sub>T</sub> /dt <sub>cr</sub> | $      f = 0500 \text{ Hz}, \\ T_j = 125 \ ^\circ\text{C}, \\ I_T = 5000 \text{ A}, \\ V_D = 2800 \text{ V}, \\ I_{TM} \leq 7000 \text{ A} $ |     |     | 1000 | A/µs |

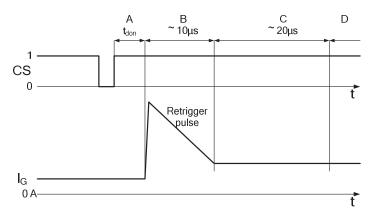

| Turn-on delay<br>time                           | t <sub>don</sub>                  | V <sub>D</sub> = 2800 V,                                                                                                                     |     |     | 4    | μs   |

| Turn-on delay<br>time status<br>feedback        |                                   | $T_{j} = 125 \text{ °C}$<br>$I_{T} = 4000 \text{ A},$<br>$di/dt = V_{D} / L_{i}$<br>$L_{i} = 3 \mu H$                                        |     |     | 7    | μs   |

| Rise time                                       | t,                                | C <sub>cL</sub> = 20 μF,                                                                                                                     |     |     | 1    | μs   |

| Turn-on energy<br>per pulse                     |                                   | $L_{CL} = 0.3 \ \mu H$                                                                                                                       |     |     | 1.8  | J    |

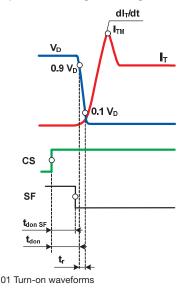

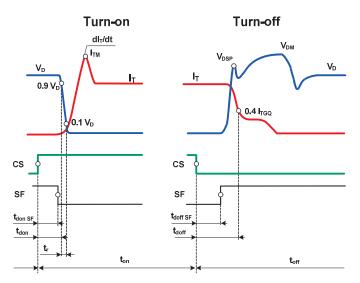

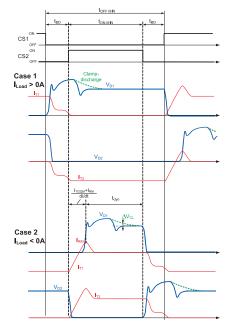

The definitions of turn-on switching parameters are illustrated on the last page(s) of the IGCT data sheets, with typical anode voltage and current waveforms along with electrical commandsignal (CS) and status-feedback signal (SF). These waveforms are reproduced in Fig. 1 and Fig. 2 shows the test circuit.

Hitachi Energy Switzerland Ltd. Semiconductors Fabrikstrasse 3 5600 Lenzburg, Switzerland Tei: +41 58 586 10 00 salesdesksem@hitachienergy.com

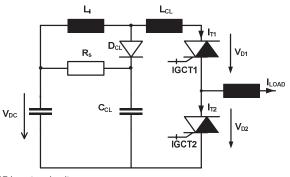

02 Turn-on test circuit

di<sub>r</sub>/dt<sub>cr</sub>: The maximum permissible on-state di<sub>r</sub>/dt at turn-on. The maximum di<sub>r</sub>/dt is very much gate current dependent (rate-of-rise-of-gate-current, di<sub>G</sub>/dt and peak gate current amplitude  $I_{GM}$ ). A large gate current ensures that all IGCT cathode segments are turned on simultaneously and within a short time ensuring fast, uniform conduction and avoiding localized conduction and «hot spots», which could destroy the IGCT. In most applications, turn-on of the IGCT causes a diode turn-off. The maximum diode turn-off di/dt usually limits the allowed rate of commutation. The turn-on gate conditions (di<sub>G</sub>/dt,  $I_{GM}$ ) of the gate-unit are designed to amply cover the (turn-off) di/dt capabilities of fast switching diodes. It would be possible to realize higher di<sub>r</sub>/dt<sub>cr</sub> for the IGCT but this would unnecessarily increase the losses, input power and cooling requirements of the gate-unit.

$t_{don,} t_{don SF'} t_r$ : Turn-on delay time, turn-on delay time status-feedback and anode voltage fall time, respectively. These definitions are illustrated in Fig. 1.

$$\begin{split} & E_{on}: \text{Turn-on energy per pulse } E_{on} \text{ is defined as the time integral of} \\ & \text{power P}(t) = I_{T}(t) \ x \cdot V_{D}(t) \text{ during turn-on (from start of commutation until } V_{D} \text{ reaches the static on-state } V_{T}): \end{split}$$

$$E_{on} = \int I_T(t) \cdot V_D(t) dt$$

The turn-on power losses,  $\mathsf{P}_{_{turn-on}}$  of the IGCT, are calculated as follows:

$$P_{turn-on} = f \cdot E_{on}$$

where *f* is the switching frequency.

We reserve the right to make technical changes or modify the contents of this document without prior notice. With regard to purchase orders, the agreed particulars shall prevail. Hitachi Energy Ltd. does not accept any responsibility whatsoever for potential errors or possible lack of information in this document.

### 2.4.3. Turn-off switching

### Maximum rated values

| Parameter                                   | Symbol             | Conditions                                                                                                                            |                                                            | max  | Unit |

|---------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------|------|

| Max.<br>controllable<br>turn-off<br>current | I <sub>tgqm1</sub> | $V_{DM} \le V_{DRM} \\ T_{j} = 0125 \ ^{\circ}\Omega \\ R_{s} = 0.35 \ ^{\circ}\Omega \\ C_{CL} = 20 \ \mu F \\ C_{CL} = 20 \ \mu F $ | $V_{\rm D} = 2800$ V<br>t <sub>on</sub> > 100 µs           | 5000 | A    |

| Max.<br>controllable<br>turn-off<br>current | I <sub>tgqm2</sub> | L <sub>CL</sub> ≤ 0.3 µH<br>f = 0300 Hz2)<br>D <sub>FWD</sub> = D <sub>CL</sub><br>= 5SDF 10H4503                                     | $V_{D} = 2800$<br>V<br>40 µs < t <sub>on</sub><br>< 100 µs | 4000 | A    |

#### Characteristic values

| Parameter                                 | Symbol               | Conditions                                                                               | min | typ  | max  | Unit |

|-------------------------------------------|----------------------|------------------------------------------------------------------------------------------|-----|------|------|------|

| Turn-off delay<br>time                    | t<br><sub>doff</sub> | V <sub>D</sub> = 2800 V<br>T <sub>j</sub> = 125 °C                                       |     |      | 8    | μs   |

| Turn-off delay<br>time status<br>feedback | $t_{\rm dffSF}$      | $V_{DM} \le V_{DRM}$<br>$R_{s} = 0.35 \Omega$<br>$I_{TGQ} = 4000 A$<br>$L_{s} = 3 \mu H$ |     |      | 7    | μs   |

| Turn-off<br>energy per<br>pulse           | E <sub>off</sub>     |                                                                                          |     | 26.5 | 31.5 | J    |

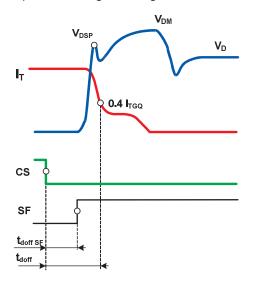

The definitions of the turn-off switching parameters, are illustrated on the last page(s) of the IGCT data sheets, with typical anode voltage and current waveforms along with the electrical command-signal and status-feedback signal. These waveforms are reproduced in Fig. 3 and Fig. 4 shows the test circuit.

03 Turn-off waveforms

Hitachi Energy Switzerland Ltd. Semiconductors Fabrikstrasse 3 5600 Lenzburg, Switzerland Tel: +41 58 586 10 00 salesdesksem@hitachienergy.com

04 Turn-off test circuit

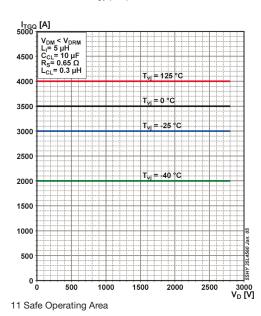

$I_{\text{TGQM}}$  is the maximum anode current that can be turned-off under the specified conditions. The value of  $I_{\text{TGQM}}$  depends on commutation voltage  $V_{\rm p}$ , junction temperature  $T_{\rm vj}$  and the on-time ton. These dependencies are specified in the diagram «Safe Operating Area» of the data sheet (see Fig. 11). Turn-off switching outside the safe operating area must be avoided. It may lead to immediate failure even for a single event.

All asymmetric and reverse conducting IGCTs are specified with a «clamp circuit» that limits the voltage but not the dv/dt. This type of di/dt snubber is normally used in voltage-source inverters (VSI). Reverse blocking IGCTs are specified with an R-C snubber, which additionally limits the dv/dt at turn-off. This is a typical snubber for current source inverters (CSI). A low snubber or clamp-inductance is necessary to limit the over-voltage spike  $V_{\rm DSP}$ . Excessive  $V_{\rm DSP}$  can lead to dynamic avalanche breakdown of the GCT and excessive losses.

$t_{\text{doff}}, t_{\text{doff SF}}$ : Turn-off delay time and turn-off delay time status-feed-back respectively. These definitions are given in Fig. 3. For more information on the status-feedback see application note 5SYA 2031 «Applying IGCT gate units».

$E_{off}$ : Turn-off energy per pulse  $E_{off}$  is defined as the time integral of the power P(t) = I<sub>T</sub>(t) x · V<sub>D</sub>(t) during turn-off (from start of commutation until I<sub>T</sub> reaches the static leakage current value):

$$E_{off} = \int I_T(t) \cdot V_D(t) dt$$

The turn-off power losses, Pturn-off, are calculated as follows:

$$P_{turn-off} = f \cdot E_{off}$$

where f is the switching frequency.

We reserve the right to make technical changes or modify the contents of this document without prior notice. With regard to purchase orders, the agreed particulars shall prevail. Hitachi Energy Ltd. does not accept any responsibility whatsoever for potential errors or possible lack of information in this document.

$E_{\rm off}$  can be varied to a certain extent by electron and/or proton irradiation as described earlier in this section for  $V_{\rm T}$ .  $E_{\rm off}$  varies, to a first approximation, linearly with  $I_{\rm TGO}$  and  $V_{\rm D}$ . It is also highly dependent on  $T_{\rm vi}$ .

### 2.5. Gate unit data

The important aspects of the gate unit are described in detail in Application note 5SYA 2031 «Applying IGCT gate units».

### 2.5.1. Power supply

### Maximum rated values

| Parameter                                           | Symbol               | Conditions                                                                                                      | min | typ | max | Unit |

|-----------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Gate unit voltage<br>(Connector X1)                 | $V_{\rm gin, RMS}$   | AC square wave<br>amplitude (15 kHz-<br>100kHz) or DC<br>voltage. No<br>galvanic isolation<br>to power circuit. | 28  |     | 40  | V    |

| Min. current<br>needed to power<br>up the Gate unit | I <sub>GIN Min</sub> | Rectified average<br>current see<br>application note<br>5SYA 2031                                               | 2   |     |     | A    |

| Gate unit power consumption                         | $P_{_{GINMax}}$      |                                                                                                                 |     |     | 130 | W    |

### Characteristic values

| Parameter                      | Symbol               | Conditions                                               | min | typ | max | Unit |

|--------------------------------|----------------------|----------------------------------------------------------|-----|-----|-----|------|

| Internal current<br>limitation | I <sub>GIN Max</sub> | Rectified average<br>current limited by<br>the Gate unit |     |     | 8   | A    |

$V_{\text{GIN,RMS}}$ : The gate unit supply voltage is the input voltage range within which the gate unit should be operated.

${\rm I}_{_{\rm GIN\,\,Min}}$  : The minimum supply current that is required to power up the gate unit properly.

$\mathsf{P}_{_{\text{GIN}\,\text{Max}}}$  . The maximum gate unit supply power that is allowed for operation.

$I_{_{GIN\,Max}}$ : The gate unit's internal power supply has a current limitation that limits the supply current to this value.

### 2.5.2. Optical control input/output

Maximum rated values

| Parameter     | Symbol           | Conditions | min | typ | max | Unit |

|---------------|------------------|------------|-----|-----|-----|------|

| Min. on-time  | t <sub>on</sub>  |            | 40  |     |     | μs   |

| Min. off-time | t <sub>off</sub> |            | 40  |     |     | μs   |

Hitachi Energy Switzerland Ltd. Semiconductors Fabrikstrasse 3 5600 Lenzburg, Switzerland Tel: +41 58 586 10 00 salesdesksem@hitachienergy.com Characteristic values

| Parameter                            | Symbol              | Conditions                              | min | typ | max  | Unit |

|--------------------------------------|---------------------|-----------------------------------------|-----|-----|------|------|

| Optical input<br>power               | $P_{onCS}$          | CS: Command<br>signal                   | -15 |     | -1   | dBm  |

| Optical noise<br>power               | $P_{offCS}$         | SF: Status<br>feedback<br>Valid for 1mm |     |     | -45  | dBm  |

| Optical output<br>power              | $P_{onSF}$          | plastic optical<br>fiber (POF)          | -17 |     | -1   | dBm  |

| Optical noise<br>power               | $P_{_{offSF}}$      |                                         |     |     | -50  | dBm  |

| Pulse width<br>threshold             | t <sub>GLITCH</sub> | Max. pulse<br>width without<br>response |     |     | 400  | ns   |

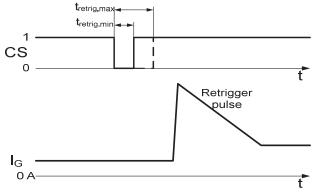

| External<br>retrigger pulse<br>width | t <sub>retrig</sub> |                                         | 700 |     | 1100 | ns   |

$t_{on}$ : The IGCT requires time to fully turn-on. Therefore, the turn-off behavior is different when the IGCT is turned on for too short a time. The specified characteristics and the turn-off capability cannot be guarantied when this minimum time is not maintained.

$t_{\mbox{\tiny off}}$  : Similar to the min. on-time, also the minimum off-time has to be maintained.

$\mathsf{P}_{_{\text{on CS}}}$  : The range of the optical power that is required to achieve a correct on-command.

$\mathsf{P}_{_{\text{off CS}}}$ : The max. optical noise power is the maximum level of the optical input power that keeps the IGCT in off-state.

P<sub>on SE</sub>: The optical power level of the feedback signal when HIGH.

$\mathsf{P}_{_{\text{off SF}}}$  : The max. optical power level of the feedback signal when LOW.

$t_{glitch}$ : The gate unit has an input filter to avoid a short disturbance on the command signal being interpreted as a switching command.

$t_{\mbox{\tiny retrig}}$  : Pulse width range of the command signal required to release a retrigger pulse.

We reserve the right to make technical changes or modify the contents of this document without prior notice. With regard to purchase orders, the agreed particulars shall prevail. Hitachi Energy Ltd. does not accept any responsibility whatsoever for potential errors or possible lack of information in this document.

### 2.5.3. Connectors <sup>2)</sup>

| Parameter                              | Symbol | Description                              |

|----------------------------------------|--------|------------------------------------------|

| Gate unit power connector              | X1     | AMP: MTA-156, Part Number<br>641210-5 3) |

| LWL receiver for command signal        | CS     | Avago, Type HFBR-2521Z <sup>4)</sup>     |

| LWL transmitter for status<br>feedback | SF     | Avago, Type HFBR-1528Z 4)                |

<sup>2</sup>) Do not disconnect or connect fiber optic cables while light is on.

<sup>3)</sup> Supplier AMP, www.amp.com

<sup>4)</sup> Supplier Avago Technologies, www.avagotech.com

This paragraph defines the optical and supply power connector. Further information can be found on the supplier websites.

### 2.5.4 Visual feedback

| Symbol | Description                                            | Color                                                                                                                                                                                          |

|--------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED1   | «Light» when GCT is off                                | (green)                                                                                                                                                                                        |

| LED2   | «Light» when gate-current is flowing                   | (yellow)                                                                                                                                                                                       |

| LED3   | «Light» when not ready /<br>Failure                    | (red)                                                                                                                                                                                          |

| LED4   | «Light» when power supply is<br>within specified range | (green)                                                                                                                                                                                        |

|        | LED1<br>LED2<br>LED3                                   | LED1       «Light» when GCT is off         LED2       «Light» when gate-current is flowing         LED3       «Light» when not ready / Failure         LED4       «Light» when power supply is |

The meaning of the visual feedback LEDs is described in the application note 5SYA 2031 «Applying IGCT gate units»

### 2.6. Thermal

Maximum rated values

| Parameter                       | Symbol           | Conditions | min | typ | max | Unit |

|---------------------------------|------------------|------------|-----|-----|-----|------|

| Junction operating temperature  | T <sub>vj</sub>  |            | 0   |     | 125 | °C   |

| Storage temperature range       | T <sub>stg</sub> |            | 0   |     | 60  | °C   |

| Ambient operational temperature | T <sub>a</sub>   |            | 0   |     | 50  | °C   |

### Characteristic values

| Parameter                                   | Symbol        | Conditions            | min | typ | max | Unit     |

|---------------------------------------------|---------------|-----------------------|-----|-----|-----|----------|

| Thermal resistance junction-to-case of GCT  | $R_{th(j-c)}$ | Double side<br>cooled |     |     | 8.5 | K/<br>kW |

| Thermal resistance case-to- heatsink of GCT | $R_{th(c-h)}$ | Double side<br>cooled |     |     | 3   | K/<br>kW |

$T_{vj}$ : The operating junction temperature. The lower limit of  $T_{vj}$  is determined mainly by the turn-on and turn-off characteristics of the IGCT. Extremely low temperatures may raise latching current to the point at which the device no longer turns on and also the turn-off capability reduces with decreasing temperature according to Fig. 11. The upper limit, on the other hand, is determined by the blocking capability of the main pn junction. Leakage current rises exponentially with temperature and thermal instabilities may start to appear at high voltage.

$\rm T_{stg}$ : The storage temperature range for short-term events. To maximize the storage life time we recommend storage at a stable temperature of 20 °C  $\pm$  10 °C and a relative humidity below 55%.

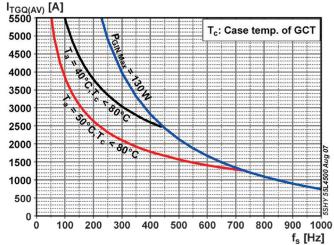

$T_a$ : The operating ambient temperature.  $T_a$  defines the temperatures at which the gate unit works reliably.  $T_a$  is the air temperature around the gate-unit components (especially the electrolytic capacitors) during operation. Temperatures below  $T_a$  min reduce  $I_{TGQM}$  because of an increase in gate unit impedance.  $T_a$  max is the ambient temperature at which ageing of the gate unit becomes important. For a lifetime of 20 years, the 60 °C case temperature of the electrolytic capacitors should be limited to 60 °C. Fig. 5 shows the effect of light forced aircooling on the allowable turn-off current as a function of switching frequency. In cases where  $T_a$ ,  $T_{case}$  GCT or cooling conditions differ significantly from the data sheet, we recommend measuring the case temperature of the electrolytic capacitors.

The operating range is also limited by the power supply capability of the gate unit. This is shown by the curve  $P_{_{GIN\,Max}}$ .

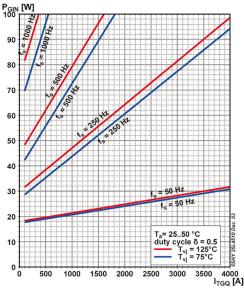

05 Max. turn-off current vs. frequency for lifetime operation (example 5SHY 55L4500)

Max. turn-off current for lifetime operation

- calculated lifetime of on-board capacitors 20 years

- with slightly forced air cooling (air velocity > 0.5 m/s)

- strong air cooling allows for increased ambient temperature

We reserve the right to make technical changes or modify the contents of this document without prior notice. With regard to purchase orders, the agreed particulars shall prevail. Hitachi Energy Ltd. does not accept any responsibility whatsoever for potential errors or possible lack of information in this document. We reserve all rights in this document and in the subject matter and illustrations contained therein. Any reproduction, disclosure to third parties or utilization of its contents – in whole or in parts – is forbidden without prior written consent of Hitachi Energy Ltd.

Hitachi Energy Switzerland Ltd. Semiconductors Fabrikstrasse 3 5600 Lenzburg, Switzerland Tel: +41 58 586 10 00 salesdesksem@hitachienergy.com  $R_{tn(i-c)}$ : Thermal resistance from junction (silicon wafer) to case with double-side cooling. As a free-floating IGCT has several dry interfaces inside the ceramic housing, it is evident that  $R_{th(i-c)}$  depends on  $F_m$ . Data sheet figures are, therefore, based on the nominal mounting force as specified in the mechanical-data sub- section. Reverse-conducting IGCTs have two separately specified values, one for the GCT-part and one for the diode-part. The data are specified under the condition that the GCT and diode parts are at the same temperature. Homogeneous mounting pressure is vital for reliable IGCT operation; this is particularly important for  $R_{tn(i-c)}$ .

$R_{th(c\cdoth)}$ : Thermal resistance from case to heat sink (surface of IGCT housing to surface of heat sink) is defined at nominal mounting force  $F_{m}$ . Since  $R_{th(c-h)}$  is a dry interface between two surfaces, it depends a great deal on the quality of the surfaces and the homogeneity of the mounting pressure. The specified  $R_{th(c-h)}$  is achieved when the heat sink surface is of a similar quality to that of the IGCT surface i.e. when its flatness is of the order of 15  $\mu$ m, its roughness is of the order of 1  $\mu$ m and the per-unit-area mounting pressure is uniform across the surface to within  $\pm$  15 %. The latter requirement calls for careful design of the clamping system are described in application note 5SYA 2036 «Recommendations regarding mechanical clamping of press pack high power semiconductors».

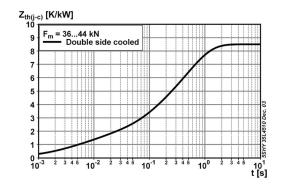

$Z_{\text{th(j-c)(t)}}$ . Transient thermal impedance,  $Z_{\text{th(j-c)(t)}}$ , emulates the rise of junction temperature versus time, when a constant power is dissipated in the junction. It is defined as the temperature difference junction-to-case, divided by the power:

$$Z_{th(j-c)}(t) = \frac{\Delta T_{(j-c)}(t)}{P}$$

Analytical function for transient thermal impedance:

| $Z_{th(j)}$           | - c)(t) = | i(1-e <sup>-</sup> | t/τ i ) |        |

|-----------------------|-----------|--------------------|---------|--------|

| i                     | 1         | 2                  | 3       | 4      |

| R <sub>i</sub> (K/kW) | 5.562     | 1.527              | 0.868   | 0.545  |

| $\tau_{i}(s)$         | 0.5119    | 0.0896             | 0.0091  | 0.0024 |

06a Exponential terms

Hitachi Energy Switzerland Ltd.

salesdesksem@hitachienergy.com

5600 Lenzburg, Switzerland

Tel: +41 58 586 10 00

Semiconductors

Fabrikstrasse 3

06b Transient thermal impedance (junction-to- case) vs. time (max. values)

This function can be specified as a curve as shown in Fig. 6b, or by an analytical approximation with the superposition of four exponential terms (Fig. 6a), as shown above. The analytical expression is particularly useful for computer calculations.

### 2.7. Diagrams

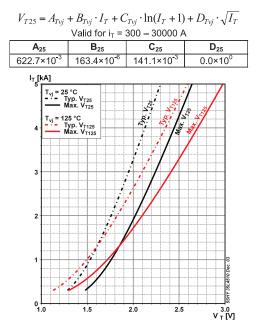

#### 2.7.1. GCT on-state current vs. on-state voltage

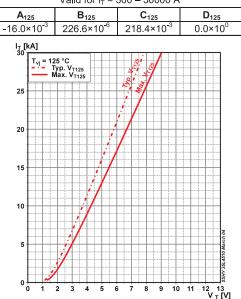

Figs. 7a and 7b show on-state voltage as a function of on-state current for  $T_{vi} = 25$  °C and 125 °C. Both, typical and maximal values are given. These curves can be used to calculate on-state losses. The max. curves are characterized by the equations shown above the diagrams.

07a GCT on-state voltage characteristics: Equation for  $T_{\rm v}j$  = 25  $^{\circ}C$  and diagram up to 6 kA

We reserve the right to make technical changes or modify the contents of this document without prior notice. With regard to purchase orders, the agreed particulars shall prevail. Hitachi Energy Ltd. does not accept any responsibility whatsoever for potential errors or possible lack of information in this document. We reserve all rights in this document and in the subject matter and illustrations contained therein. Any reproduction, disclosure to third parties or utilization of its contents – in whole or in parts – is forbidden without prior written consent of Hitachi Energy Ltd.

10

$$\begin{split} V_{T125} = A_{Tvj} + B_{Tvj} \cdot I_T + C_{Tvj} \cdot \ln(I_T + 1) + D_{Tvj} \cdot \sqrt{I_T} \\ \text{Valid for } i_{\mathsf{T}} = 300 - 30000 \text{ A} \end{split}$$

07b GCT on-state voltage characteristics: Equation for  $T_{\rm v} j$  = 125  $^\circ C$  and diagram up to 30 kA

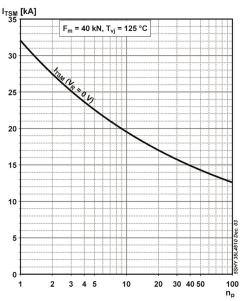

### 2.7.2. GCT surge current vs pulse width and number of pulses

Figs. 8 and 9 specify the surge current ratings and corresponding fusing integrals. The relationship between these two ratings was examined in the on-state parameter section. The constraints linked to  $I_{\text{TSM}}$  and  $\int i^2 t$  mentioned there also apply to Fig. 9.

The maximum  $I_{TSM}$  shown in Fig. 8 should not be exceeded even for shorter pulses. For surge current requirements that do not resemble a sine half wave or cannot be covered by a sine half wave shown in Fig. 8, please contact your nearest representative or the address shown at the end of this application note for evaluation.

08 Surge on-state current vs. pulse length, half- sine wave. No reapplied voltage

$09\ {\rm Surge}$  on-state current vs. number of pulses, half-sine wave,  $10\ {\rm ms},\ 50{\rm Hz}.$  No reapplied voltage

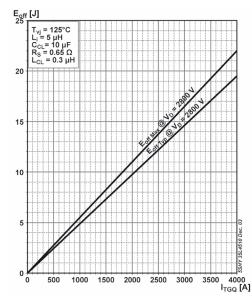

### 2.7.3. GCT turn-off characteristics

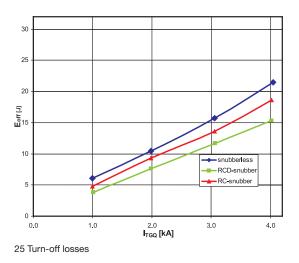

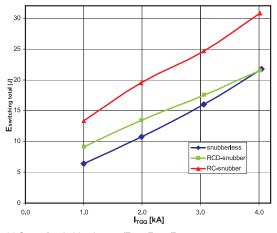

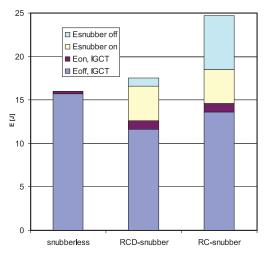

Fig. 10 shows GCT turn-off losses vs turn-off current. The curves are determined in the test circuit of the data sheet. In VSI topologies with clamp circuits, the losses vary approximately linearly with DC-link voltage  $V_{\rm p}$  and turn-off current  $I_{\rm reg}.$

Hitachi Energy Switzerland Ltd. Semiconductors Fabrikstrasse 3 5600 Lenzburg, Switzerland Tel: +41 58 586 10 00 salesdesksem@hitachienergy.com We reserve the right to make technical changes or modify the contents of this document without prior notice. With regard to purchase orders, the agreed particulars shall prevail. Hitachi Energy Ltd. does not accept any responsibility whatsoever for potential errors or possible lack of information in this document.

Fig. 10 specifies the turn-off safe operating area in a VSI clampcircuit. Two parameters mainly determine the turn-off capability:

- a) the impedance of the turn-off gate channel increases with decreasing ambient temperature of the gate unit; this limits max. turn-off current  $I_{TGOM}$  independently of turn-off voltage

- b) The max. turn-off power capability of the GCT limits turn-off current as a function of turn-off voltage.

For these reasons, the safe operating area (Fig. 11) depends on device type and varies according to the dominant constraint (gateunit type, DC voltage, temperature etc).

10 GCT turn-off energy per pulse vs. turn-off current

### 2.7.4. Gate unit related diagrams Power consumption

The total power consumption of the IGCT gate unit is strongly load-dependent as can be seen in Fig. 12. Turn-off current I<sub>TGQ</sub>, switching frequency fs, junction temperature T<sub>vj</sub> and device technology (gate charge Q<sub>gq</sub>) have a major influence on power consumption. The power supplied to the gate-unit falls into two parts:

- a) a small thermal dissipation in the gate circuit and in the gatecathode junction; this is dependent on switching frequency and ambient temperature since the «back-porch» current is increased at low temperature to ensure latching.

- b) the bulk of the supplied power is transferred to the load once the cathode is commutated off.

Gate unit limitations must be checked before the operating range in a specific application is determined. For the thermal limitations see Fig. 5.

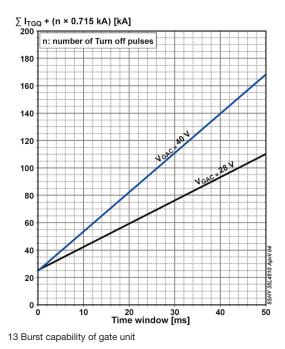

The gate unit of the IGCT has a large capacitor bank which stores energy for turn-on pulse, back-porch current and turn-off pulse. Since the turn-off pulse needs a large charge and the gate unit power supply has an internal current limitation ( $I_{GIN Max}$ ), triggering with very high frequencies is limited according to Fig. 13. The diagram shows only the limitation of the gate unit. Independent of this the minimum on- and off-times ( $t_{on}, t_{off}$ ) have to be maintained. Also the junction temperature of the GCT has to be taken into account. Thus the burst capability may be limited by the switching losses in the IGCT rather than the gate unit.

### **Burst capability**

12 Max. gate unit input power in chopper mode

We reserve the right to make technical changes or modify the contents of this document without prior notice. With regard to purchase orders, the agreed particulars shall prevail. Hitachi Energy Ltd. does not accept any responsibility whatsoever for potential errors or possible lack of information in this document. We reserve all rights in this document and in the subject matter and illustrations contained therein. Any reproduction, disclosure to third parties or utilization of its contents – in whole or in parts – is forbidden without prior written consent of Hitachi Energy Ltd.

Hitachi Energy Switzerland Ltd.

salesdesksem@hitachienergy.com

5600 Lenzburg, Switzerland

Tel: +41 58 586 10 00

Semiconductors

Fabrikstrasse 3

# 2.8. Diode-specific data of reverse conducting IGCTs (from data sheet 5SHX 26L4520)

### 2.8.1. Diode on-state

On-state data and diagrams are described in the same way as the on-state data of the GCT-part. Please refer to section 3.4.1 and diagrams Fig. 6 ... 9.

### 2.8.2 Diode turn-on

| Parameter             | Symbol    | Conditions                                                    | min | typ | max | Unit |

|-----------------------|-----------|---------------------------------------------------------------|-----|-----|-----|------|

| Peak forward recovery | $V_{FRM}$ | dl <sub>F</sub> /dt=650 A/µ<br>T <sub>vj</sub> = 125 °C       |     |     | 80  | V    |

| voltage               |           | dl <sub>F</sub> /dt=3000 A/<br>µs<br>T <sub>vj</sub> = 125 °C |     |     | 250 | V    |

V<sub>FRM</sub>: Peak forward recovery voltage: Please refer section 4.1.6.

### 2.8.3. Diode turn-off

Maximum rated values Parameter Symbol Conditions Unit min typ max I<sub>FM</sub> = 2200 A Max. decay 650 A/µs di/dt = 125 °C rate of on-state ′ = 2800 V current I<sub>FM</sub> = 3200 A Max. decay 650 A/us di/dt<sub>crit</sub> T<sub>vj</sub> = 125 °C rate of on-V<sub>DClink</sub> = 2800 V state

Hitachi Energy Switzerland Ltd. Semiconductors

current

Fabrikstrasse 3 5600 Lenzburg, Switzerland Tel: +41 58 586 10 00 salesdesksem@hitachienergy.com Characteristic values

| Parameter                      | Symbol          | Conditions                                                                                                  | min | typ | max  | Unit |

|--------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| Reverse<br>recovery<br>current | I <sub>RM</sub> | $I_{FM} = 2200 \text{ A}$<br>$V_{DClink} = 2800 \text{ V} - dI_{F'}$<br>$dt = 650 \text{ A}/\mu\text{s}$    |     | 900 |      | A    |

| Reverse<br>recovery<br>charge  | Q <sub>rr</sub> | $C_{CL} = 10 \ \mu F$<br>$R_{s} = 0.65 \ \Omega$<br>$T_{vj} = 125 \ ^{\circ}C$<br>$D_{cl} = 5SDF \ 10H4503$ |     |     | 2800 | μC   |

| Turn-off<br>energy             | E <sub>rr</sub> | CL                                                                                                          |     | 2.7 | 4    | J    |

di/dt<sub>crit</sub>: Max. decay rate of on-state current defines the minimum value of (L<sub>i</sub> + L<sub>cl</sub>) according to:

$$(L_i + L_{CL}) = \frac{V_{DClink}}{di/dt}$$

where V<sub>DClink</sub> is the voltage drop across (L<sub>1</sub> + L<sub>CL</sub>) during turn-off of the diode (see Fig. 4 for test circuit). It is important to respect the «diode safe operating area» diagram of the data sheet and to ensure that L<sub>CL</sub> be as low as possible. Typical applications work in a range of L<sub>CL</sub> = 150 ... 250 nH. Large stray clamp inductance increases the electrical stress on the diode during turn-off and also reduces the turn-off capability of the switch.

$I_{_{RM}}$ ,  $Q_{_{rr}}$ ,  $E_{_{rr}}$ : Reverse recovery current, reverse recovery charge and diode turn-off energy are specified under application-specific conditions. Additional data is available in the data sheet diagrams.

### 2.8.4. Thermal data

In addition to the thermal data of the IGCT, the data sheets of reverse conducting IGCTs have thermal data for the diode part. The data is documented in the same way as in section 2.6.  $R_{th}$  and  $Z_{th}$  are specified without heat flow between the GCT-part and diode-part.

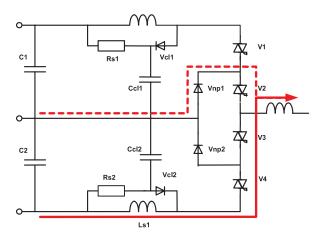

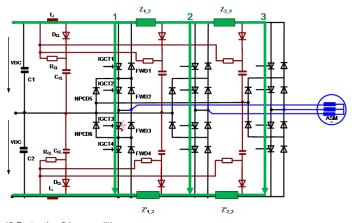

### **3. IGCT application-specific topics** 3.1 IGCTs in Voltage Source Inverters (VSI)

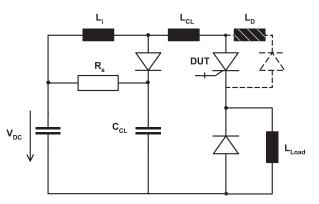

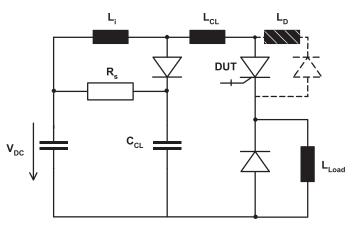

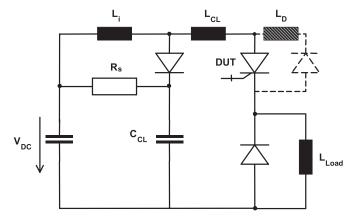

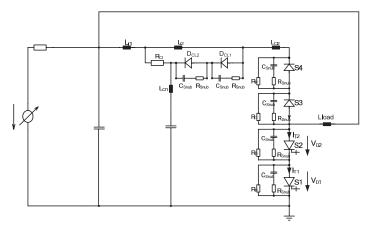

Reverse conducting IGCTs (RC-IGCT), asymmetric IGCTs (AS-IGCT) and their corresponding diodes are qualified and tested in test circuits built according to the circuit diagram below. It is an equivalent circuit for the switching events occurring in a VSI circuit, be it of 2-level or 3-level topology.

We reserve the right to make technical changes or modify the contents of this document without prior notice. With regard to purchase orders, the agreed particulars shall prevail. Hitachi Energy Ltd. does not accept any responsibility whatsoever for potential errors or possible lack of information in this document.

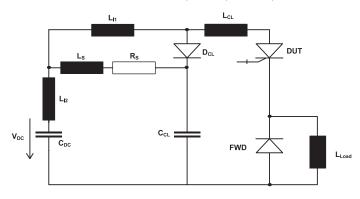

14 Test circuit as shown in the data sheet

15 General current and voltage waveforms with IGCT-specific symbols

### 3.1.1. Design criteria

For the design of an inverter, several considerations have to be taken into account. The main concerns are:

- Critical di/dt of the freewheeling diode: In order to meet the turn-off di/dt requirements of the freewheeling diode, the turn-on di/dt of the IGCT has to be limited.

- Minimum dead times  $t_{_{\rm ON\,MIN}}$  and  $t_{_{\rm OFF\,MIN}}$

See Fig. 17 and 18. For the control scheme, the dead time between switching transients should be as small as possible. On the other hand, IGCTs should not be turned on or turned off whilst the clamp circuit is still conducting. Due to the blocking delay time tBD, which is the necessary delay time between turn-off and turn-on of a switching pair within a VSI phase leg,  $t_{\text{ON MIN}}$  and  $t_{\text{OFF MIN}}$  are not equal:

16 Minimum dead times  $t_{_{\text{ON MIN}}}$  and  $t_{_{\text{OFF MIN}}}$

$$t_{OFF MIN} = t_{ON MIN} + 2 \times t_{BD} \qquad \text{with} \qquad t_{ON MIN} \ge \frac{I_{TGOM} + I_{RM}}{di/dt} + t_{dym}$$

In IGCT circuits, a blocking-delay-time  $t_{_{BD}}$  of about 10 µs is typical. These restrictions are due to the conditions of the clamp circuit. However there are also restrictions because of the IGCT itself. This is because the GCT needs time to reach its steady state. Therefore, it is mandatory to maintain the minimum on and off-times  $t_{_{ON}}$  and  $t_{_{OFF}}$  in the data sheet. If these minimum times are violated, the specified SOA of the device may not be met.

### Maximum device voltage $\mathbf{V}_{_{\mathrm{DM}}}$

The voltage overshoot  $V_{_{\rm DM}}$  is not allowed to exceed the rated

Hitachi Energy Switzerland Ltd. Semiconductors Fabrikstrasse 3 5600 Lenzburg, Switzerland Tel: +41 58 586 10 00 salesdesksem@hitachienergy.com We reserve the right to make technical changes or modify the contents of this document without prior notice. With regard to purchase orders, the agreed particulars shall prevail. Hitachi Energy Ltd. does not accept any responsibility whatsoever for potential errors or possible lack of information in this document.

repetitive blocking voltage of either the IGCT or the diode:

$V_{\rm DM} < V_{\rm DRM}, V_{\rm RRM}$

The voltage overshoot is also important because of cosmic ray. In some designs the cosmic ray failure rate due to this over-voltage can become dominant compared to the dc-link voltage. The reason for this is that the cosmic failure rate increases disproportionally to the applied voltage. For more information to this topic, please consult application note 5SYA 2046 «Failure rate of IGCTs due to cosmic ray»

### Clamp voltage overshoot $\Delta VC_L$

To stay within the safe operating area of IGCTs and diodes, the clamping capacitor voltage transient  $\Delta V_{\rm CL}$  must be close to zero again before the next switching transition takes place. If this condition is not fulfilled, the switching voltage V<sub>D</sub> will be higher than V<sub>DC</sub> and may exceed max. V<sub>D</sub> of the data sheet (see Fig. 11).

### Clamp diode current I

Not only the clamping capacitor over-voltage, but also the clamping diode current,  $I_{DCL}$ , must be close to zero before the IGCT turns on again. If not, the clamping diode, at IGCT turn-on, will itself turn-off at a high di/dt value (limited by the stray inductance  $L_{CL}$  only) in excess of the di/dt capability of the clamping diode.

### 3.1.2. Determining the design parameters

The values for L<sub>i</sub>,  $C_{CL}$  and  $R_s$  given in the conditions column of the data sheet are established values and can be used as a starting point for the design. However, these values do not consider the parasitic parameters that are present in all real applications. Figure 18 depicts the test circuit as in the data sheet but extended to show the most important parasitic parameters.

18 Circuit as shown in the data sheet, extended with parasitic inductances

C<sub>DC</sub>

$R_s$

$L_{s}$

C

L<sub>CL</sub>

D<sub>CI</sub>

DC-link capacitor

di/dt limiting inductor; the di/dt limiting inductor  ${\rm L}_{\!_{\rm I}}$  is normally divided in two parts:

$L_{_{11}}$ : discrete inductor to achieve the required di/dt  $L_{_{12}}$ : stray inductance of the DC-link capacitor; this part is not damped by  $R_{_{S}}$  and therefore strongly contributes to the voltage overshoot  $V_{_{DM}}$  and should be minimized damping resistor, used to dissipate the clamp circuit energy stray inductance of damping resistor, should be minimized clamp capacitor, used to clamp the IGCT over-voltage; it also initially absorbs some of the energy stored in the di/dt limiting inductor

stray inductance of the clamp - should be minimized

clamp diode, should have a small forward recovery  $V_{_{\rm FB}}$ .

### 3.1.3. Determining the value of the di/dt limiting inductor

In a VSI, as in most power electronic circuits, a diode turn-off is caused by an IGCT turn-on and the diode's turn-off di/dt capability is, in most cases, lower than the turn-on di/dt capability of the IGCT. This is especially true in common applications without a turn-off snubber. Hence the di/dt choke  $L_1$  must be large enough to allow operation within the di/dt range of the diode even at the highest DC-link voltages. Typical values for Hitachi Energy diodes are between 200 and 1000 A/µs depending on diode wafer size and switching voltage.

Diode switching losses and surge currents are also dependent on the choke size and these considerations may require a larger inductance value. This, however, will come at the cost of a slower clamp circuit transient  $(t_{dyn})$  and longer switching dead times. The minimum size of the di/dt inductor can be calculated from the maximum dc-voltage and the maximum allowed di/dt:

$$L_{I} = L_{I1} + L_{I2} > \frac{V_{DC \max}}{di / dt_{\max}} (-L_{CL})$$

The stray inductance of the clamp ( $L_{cL}$ ) is normally disregarded.

### 3.1.4. Determining the value of the clamp capacitor $\rm C_{_{CL}}$ and the damping resistor $\rm R_{_S}$

Because of the parasitic parameters, it is difficult to determine an analytic method for calculating the optimal values for  $C_{cL}$  and  $R_s$ . We, therefore, recommend the following procedure to optimize  $C_{cL}$  and  $R_s$ :

Hitachi Energy Switzerland Ltd. Semiconductors Fabrikstrasse 3 5600 Lenzburg, Switzerland Tel: +41 58 586 10 00 salesdesksem@hitachienergy.com We reserve the right to make technical changes or modify the contents of this document without prior notice. With regard to purchase orders, the agreed particulars shall prevail. Hitachi Energy Ltd. does not accept any responsibility whatsoever for potential errors or possible lack of information in this document.

a) implement the above circuit (Fig. 17) in a circuit simulation tool, e.g. SPICE

b) use an ideal switch that changes its impedance from on-state to off-state within about 2  $\mu s$

c) chose the values of the data sheet as starting point for  $\rm C_{\tiny CL}$  and  $\rm R_{_S}$

d) insert estimated values for  $L_{\mbox{\tiny I2}}$  and  $L_{\mbox{\tiny S}}$

e) run IGCT turn-off switching simulations with worst case conditions (V $_{\rm DC},~I_{\rm TGOM}$ )

f) iteratively adjust the values of  $C_{CL}$  and  $R_s$  to obtain the desired results:

I.  $V_{DM} < V_{DRM}$  (increase  $C_{CL}$  or decrease  $R_s$ ) II. damping of loop  $R_s - C_{CL} - C_{DC} - L_{I2} - L_s$  so that the clamp diode does not conduct again after its turn-off (increase  $R_s$ )

III. clamp diode blocks before an associated IGCT switches on again

IV. clamp capacitor is discharged to its static value before an associated IGCT switches on or off again (decrease  $\rm C_{_{CL}}$  or  $\rm R_{_S})$

g) the stray inductances may differ from the anticipated values and other parameters may influence the design; the above simulations together with accurate verification measurements will ideally be part of the design iterations.

For this simulation, the turn-off behavior of the IGCT is not relevant. The IGCT can therefore be modeled as a simple ideal switch with a defined transition time. For example in SPICE, a voltage controlled switch can be used as follows:

.MODEL IGCT VSWITCH Roff=1e4 Ron=10.0e-3 Voff=0.0V Von=1.0V

This switch can then be controlled with a voltage ramp that goes from 1 V to 0 V within 5  $\mu s.$

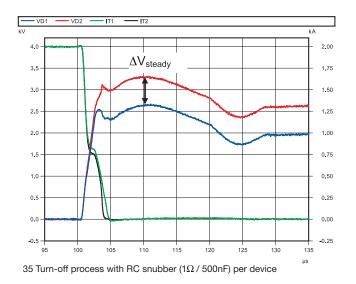

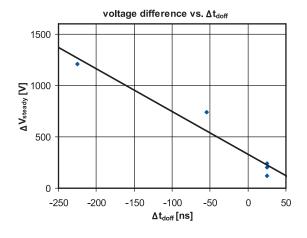

The first voltage spike in the simulation ( $V_{\text{DSP}}$ ) has to be ignored, since it is highly IGCT dependent (and not simulated by this simple model). It is also not relevant for the design of  $C_{\text{CL}}$  and  $R_{\text{s}}$ . The following figures show examples of simulated IGCT turn-off waveforms. All designs work with a 6kV device, however the allowable minimum turn-off times differ. To avoid stress on the clamp diode, the IGCT should not be switched while the clamp diode is still conducting.

In the above paragraph, the design of the clamp circuit parameters was shown for IGCT turn-off. Naturally the freewheeling diode (FWD) also needs a clamp. Whereas for the IGCT, the turn-off current determines the clamp overshoot voltage, for the freewheel diode, it is the reverse recovery current  $I_{\rm RM}$  that causes the overshoot. Since in most applications, the maximum IGCT turn-off current is larger than the maximum diode reverse recovery current, the clamp design of

the IGCT normally also suits the diode turn-off. The power losses in the damping resistor  $\rm R_s$  can be calculated with confidence from the turn-off current and the value of the di/dt limiting inductor.

$$E_{Rs} = \frac{I_{TGQ}^{2} \cdot L_{I}}{2}$$

for IGCT turn-off respectively

$$E_{Rs} = \frac{I_{RM}^{2} \cdot L_{I}}{2}$$

for diode turn-off.

This calculation only takes into account the switching events in the specific phase-leg. Since in most applications several phase-legs are connected to the same dc-link capacitor, there is an interaction between the phase-legs that may lead to additional losses in the clamp resistor.

### 3.1.5. Stray inductance L<sub>CL</sub>

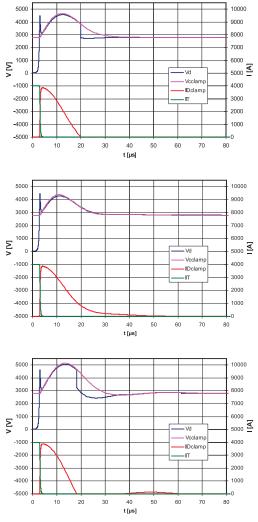

The stray inductance  $L_{CL}$  is the overall inductance in the loop comprising  $C_{CL}$ ,  $D_{CL}$ , DUT and FWD. It is determined by the geometry of bus bars, cables, heat sinks and the devices in the commutation circuit. This inductance has a major influence on the first voltage overshoot peak  $V_{DSP}$  (Fig. 15) and the switching losses of both IGCT and diode. Switching losses increase and the safe operating area decreases when the loop inductance increases. The test circuit stray inductance LC<sub>L</sub> is given for each IGCT or diode product in the data sheet.

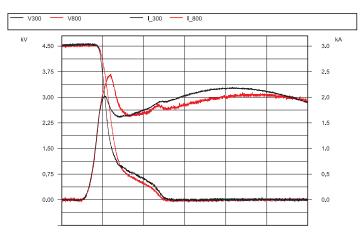

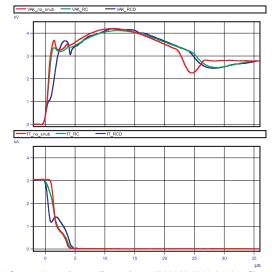

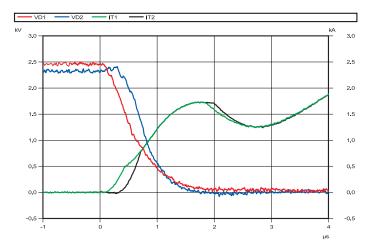

Fig.20 shows the influence of the stray inductance LCL on the switching waveforms of IGCT type 5SHY 35L4510 by comparing waveforms with 300 and 800 nH stray inductances.

As can be seen in Fig.19, the voltage overshoot increases by about 700 V. The turn-off energy in this example is 10.6 Ws (300 nH) and 12.0 Ws (800 nH).

High values of  $L_{_{CL}}$  increase the instantaneous power of the IGCT. This reduces the turn-off capability. Also the device voltage tends to snap off at the end of the tail current leading to an increased voltage overshoot and additional electromagnetic emission.

- The stray inductance L<sub>CL</sub> should be minimized

- To meet the specified SOA and switching losses, L<sub>CL</sub> has to be equal to or less than the value specified in the data sheet.

### 3.1.6 Influence of the clamp diode type

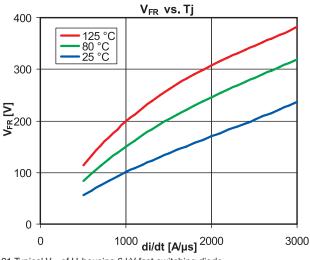

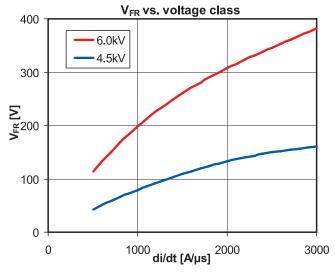

For selection of the clamp diode, the forward recovery ( $V_{FR}$ ) has to be considered. When the current from the IGCT is commutated to the clamp diode, the diode reacts with an initially higher forward voltage drop. This is because the number of free charge carriers is initially much lower than in steady state and the diode's conductivity is still low.

Hitachi Energy Switzerland Ltd. Semiconductors Fabrikstrasse 3 5600 Lenzburg, Switzerland Tel: +41 58 586 10 00 salesdesksem@hitachienergy.com We reserve the right to make technical changes or modify the contents of this document without prior notice. With regard to purchase orders, the agreed particulars shall prevail. Hitachi Energy Ltd. does not accept any responsibility whatsoever for potential errors or possible lack of information in this document.

<sup>19</sup> Determine size of clamp capacitor  $C_{cL}$  and damping resistor  $R_s$  for freewheeling diode. Clamp diode turns on for a second time;  $L_p$  is too high, the damping in the loop

L<sub>12</sub>-L<sub>5</sub>-R<sub>5</sub>-C<sub>0</sub>-C<sub>DC</sub> is too low • minimize L<sub>2</sub>

Minimum transient time  $t_{dyn} \sim 70 \ \mu s \ / \ V_{DM} = 5.0 \ kV$

The V<sub>FR</sub> is strongly dependent on the voltage class, diameter and temperature of the diode as well as the forward di/dt. Figs. 21 and 22 show typical curves for 4.5 kV and 6.0 kV Hitachi Energy's diodes with «H-housings» (68 mm wafers). The active silicon area of the diode influences  $V_{FR}$  by determining di/dt per unit area. The forward recovery behavior of the clamp diode has the same effect as stray inductance in the clamp circuit in that it increases

effect as stray inductance in the clamp circuit in that it increases the peak voltage  $\rm V_{\rm \tiny DSP}.$  The clamp design, shown in the conditions

20 Influence of stray inductance on turn-off behavior (LCL = 300 nH and 800 nH)

<sup>21</sup> Typical  $\rm V_{_{FR}}$  of H-housing 6 kV fast switching diode

column of the data sheet for I<sub>TGQM</sub> and E<sub>off</sub>, is valid for Hitachi Energy's diode of the same voltage class as the IGCT and a housing type that is one size smaller than that of the IGCT. In applications where SOA and E<sub>off</sub> are critical, it is recommended to use a clamp diode of the same voltage class as the IGCT and to minimize the clamp inductance.

Hitachi Energy Switzerland Ltd. Semiconductors Fabrikstrasse 3 5600 Lenzburg, Switzerland Tel: +41 58 586 10 00 salesdesksem@hitachienergy.com We reserve the right to make technical changes or modify the contents of this document without prior notice. With regard to purchase orders, the agreed particulars shall prevail. Hitachi Energy Ltd. does not accept any responsibility whatsoever for potential errors or possible lack of information in this document.

22 Typical  $V_{_{FR}}$  of H-housing fast switching diodes with different voltage classes

### 3.1.7. Overview of parameter influences

The following table shows which parameter influences which value in which direction, since the influence of the parameters is not obvious at first glance.

|           |                       |                    | increase of     |                 |          |    |                          |

|-----------|-----------------------|--------------------|-----------------|-----------------|----------|----|--------------------------|

|           |                       | C <sub>cl</sub>    | L <sub>I1</sub> | L <sub>I2</sub> | $L_{CL}$ | Ls | Rs                       |

|           | GCT turn-off losses   | $\mathbf{\hat{v}}$ | ⇒               | ⇒               | 22       | ⇒  | ⇒                        |

| :         | GCT turn-on losses    | ⇔                  | $\Sigma$        | Ŷ               | ⇒        | ⇔  | ⇒                        |

| on .      | FWD turn-off losses   | Ś                  | Ś               | 22              | 22       | ₽  | $\langle \gamma \rangle$ |

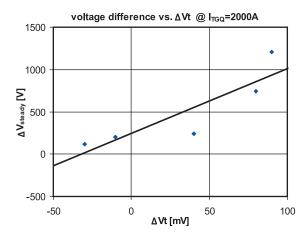

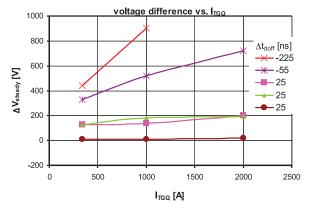

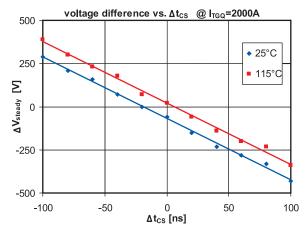

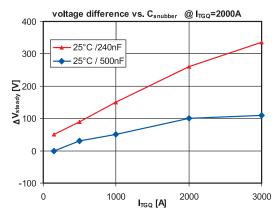

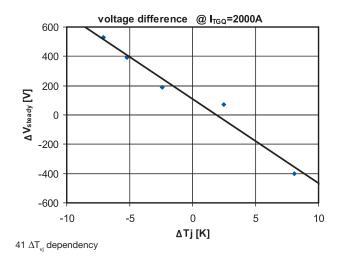

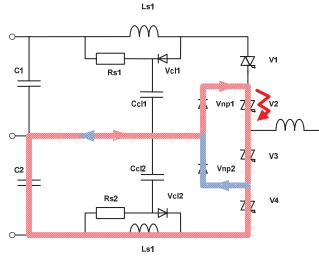

| JCe       | clamp resistor losses | ⇔                  | বর              | মম              | ⇔        | ⇔  | ⇒                        |